簡介與重要性

早期的製程因為功耗不高,因此通常會忽略功耗的問題。然而,隨著製程進步到 90 奈米後,漏電流帶來的靜態功耗顯著增加,使得功耗問題不能再忽視。

UPF 的角色

UPF(Unified Power Format)是一個用來描述 IC 設計中電源管理的標準語言,最新版本為 UPF 3.1(IEEE 1801-2018)。UPF 將設計中的電源需求與 RTL分離,幫助設計者定義和管理多電源域,使低功耗策略更靈活且易於集成。

UPF新版本有些語法會被捨棄,不一定要用到最新的3.1,用2.0甚至1.0也可以。

常見的低功耗技術像是power gating,做了之後還會再搭配isolation,retention。

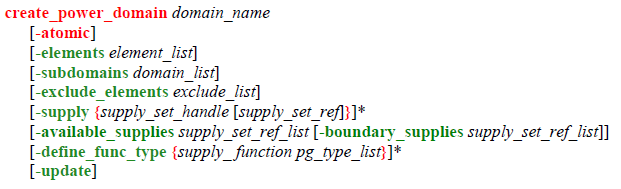

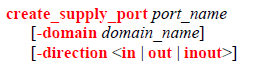

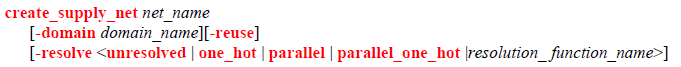

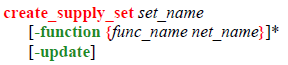

以下為 UPF 中的一些常見語法:

create_power_domain:用於定義電源域,劃分出虛擬的等電位作用範圍。

create_power_supply_port:用來定義電源或接地端口。

create_supply_net:定義電源線路。

connect_supply_net:連接電線與電源

create_supply_set:定義電源與線路的集合。

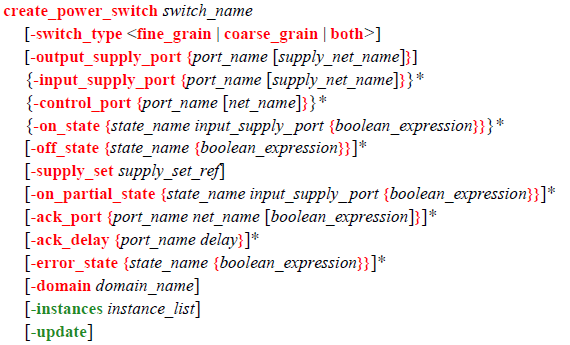

create_power_switch:定義電源開關。

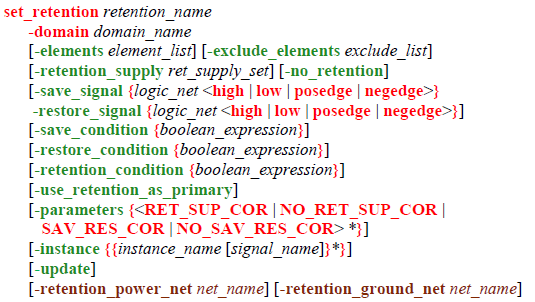

set_retention:定義在斷電期間需要保存的資料,當重新供電時,將這些資料寫回到電路,以便快速恢復到斷電前的狀態,減少重新初始化的時間和功耗。

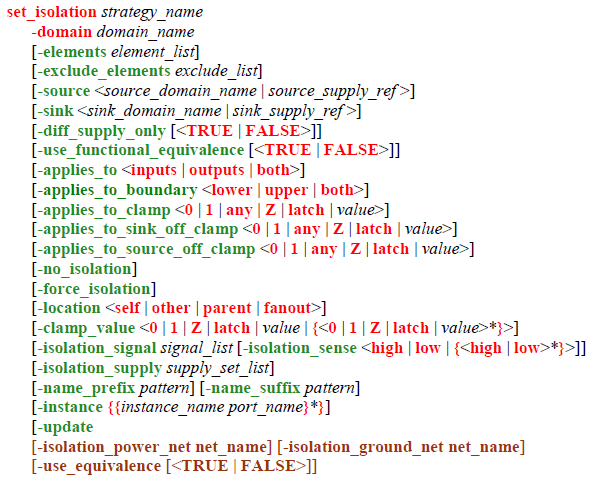

set_isolation:定義在斷電期間輸出端的固定值,以防止輸出未知或不穩定的訊號,確保其他電路不受干擾,避免整體運作受到影響。

以下的的圖片語法都是最新的UPF3.1,跟舊版的會有點差異。

create_power_domain

create_power_domain 最常用的參數是elements

要宣告為top domain

upf 2.0之後的寫法為

create_power_domain_top -elements {.}

1.0的寫法是

create_power_domain_top -include_scope

-include_scope,這個參數在2.0已經被捨棄

create_power_domain PDTop

-elements {.}

-supply {primary PDTop_s}

create_power_supply_port

direction參數通常不會寫

create_power_supply_port VDD

create_power_supply_port VSS

create_supply_net

create_supply_net VDD

create_supply_net VSS

connect_supply_net

connect_supply_net VDD -ports VDD

connect_supply_net VSS -ports VSS

create_supply_set

create_supply_set PDTop_s

-function {power VDD} -function {ground VSS}

create_power_switch

create_power_switch ps_Sel

-domain PD

-input_supply_port {VDD_in VDD}

-output_supply_port {VDD_out VDD_Sel}

-control_port {enable power_switch}

-on_state {on_state VDD_in {!enable}}

-off_state {off_state {enable}}

control_port是控制switch的訊號

on_state是power on時

off_state是pwoer off

set_retention

set_retention ret

-domain PDTop

-elements module_instance

-restore_signal {restore_signal posedge}

-save_signal {save_signal posedge}

-retention_supply PDTop_s

elements是要儲存的訊號

restore_signal是恢復供電時的觸發訊號

save_signal是斷電前要保存的觸發訊號

set_isolation

set_isolation iso

-domain PDTop

-elements module_instance/module_output

-clamp_value Z

-isolation_signal power_switch

-isolation_sense high

-isolation_supply PDTop_s

elements是要保持穩定的output訊號

clamp_value表示斷電時要為什麼值,可設為0、1、Z、latch

isolation_signal是觸發的訊號

isolation_sense是在high還是low觸發

剩下的我就不介紹了

而其他的低功耗這篇寫得很好